Il a été évoqué ici et ici l’utilisation possible d’un circuit OSD MAX7456 pour manipuler à la volée le niveau des lignes 310 et 622 d’un signal vidéo 625 lignes standard.

Le but est de pouvoir imposer des niveaux déterminés (delui du noir ou du blanc ) sur les lignes 310/622 d’un signal vidéo en clair en amont d’un décodeur pour forcer ce dernier à se comporter comme s’il était en présence d’un signal embrouillé.

Un décodeur dont les retards 0 et 2 ont été permutés décryptera ce signal vidéo à l’inverse du décodeur qu’il était avant modification et la réciprocité fera que ce décodeur précédé du circuit OSD se comportera comme un encodeur.

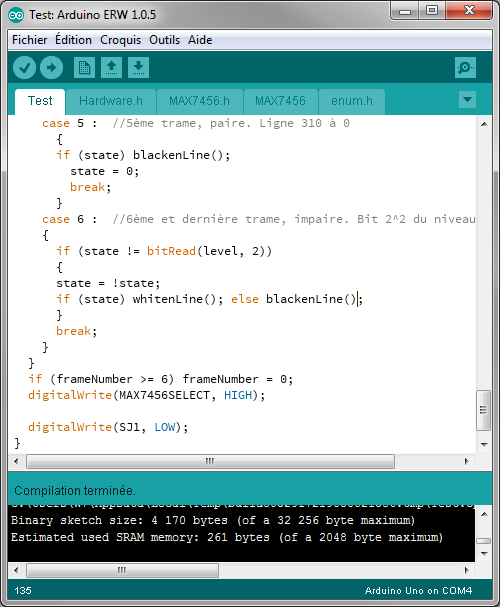

L’opération consisterait à remplir toute la mémoire OSD du MAX7456 de caractères complétement transparents sauf la dernière ligne qui le serait par deux caractères particuliers presque entièrement transparents hormis une seule rangée de pixels, en principe la dernière, qui seraient soit noirs soit blancs.

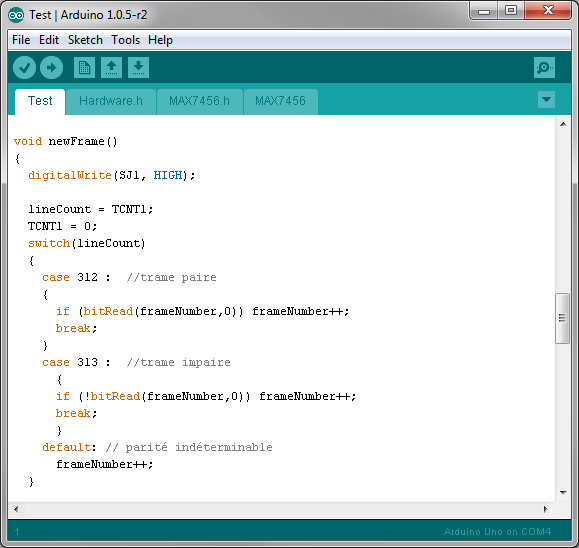

La gageure étant de faire correspondre cette rangée de pixels avec les lignes 310/622 et que l’Arduino puisse en modifier dynamiquement le niveau blanc/noir à chaque nouvelle trame.

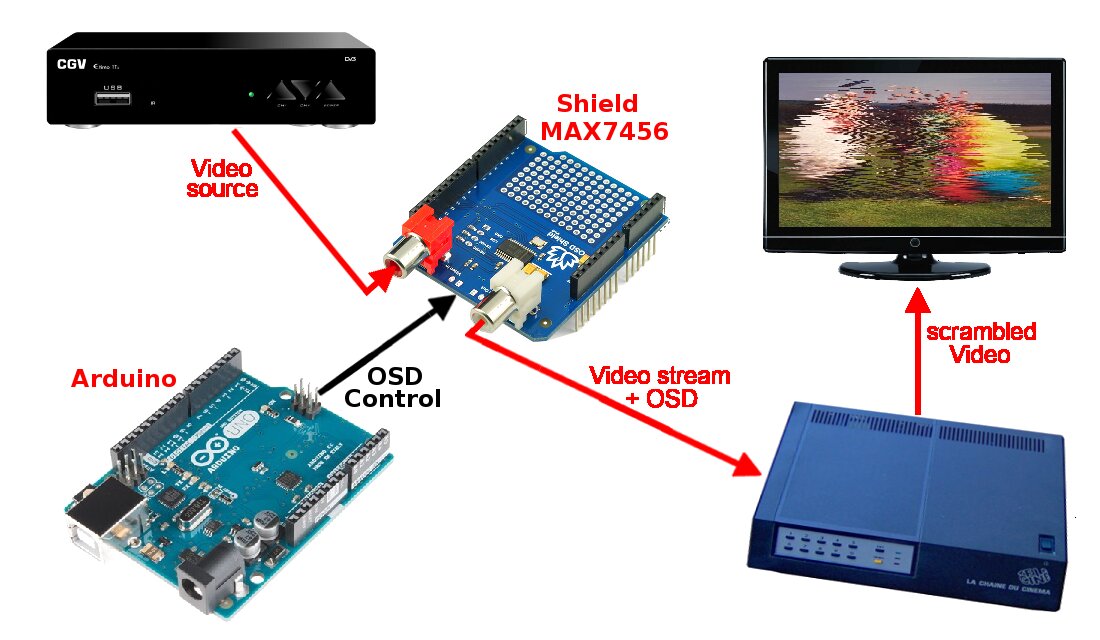

Ci-dessous, l’Illustration de ce principe basé sur un Arduino Uno équipé d’un shield OSD MAX7456 afin que le projet soit le plus « plug & play » possible :

Le shield OSD « VideoOverlayShield » de ce synoptique devrait permettre de réaliser un ensemble compact sans aucune soudure hormis les 3 ou 4 continuités nécessaires à la configuration souhaitée pour ce shield.

L’Arduino est nécessaire pour assurer :

- L’initialisation à la mise sous tension de la mémoire OSD du MAX7456,

- Le dialogue avec l’utilisateur : paramétrage du niveau de programme sur les lignes 622, reprogrammation du générateur de caractère…

- Des tâches cycliques comme le comptage des impulsions de synchronisation ligne, le traitement des interruptions provoquées par la synchronisation trame, le rafraichissement de la dernière ligne de la mémoire OSD à chaque nouvelle trame…

Ci-dessous un « VideoOverlayShield » embroché sur un Arduino Uno, l’ensemble est inséré entre une source vidéo et un moniteur et leur alimentation est assurée par le bus USB connecté sur un PC. L’ensemble peut aussi être indépendant car l’Arduino possède un jack pour y connecter une source continue extérieure dont la tension est comprise entre 7 et 12 volts :

Toujours dans le même objectif d’une réalisation la plus « plug & play » possible, il existe une autre alternative avec la carte support « click shield » conçue pour y enficher 2 cartes filles de la collection « Click Boards » dont la carte OSD « OSD click » équipée d’un MAX7456 :

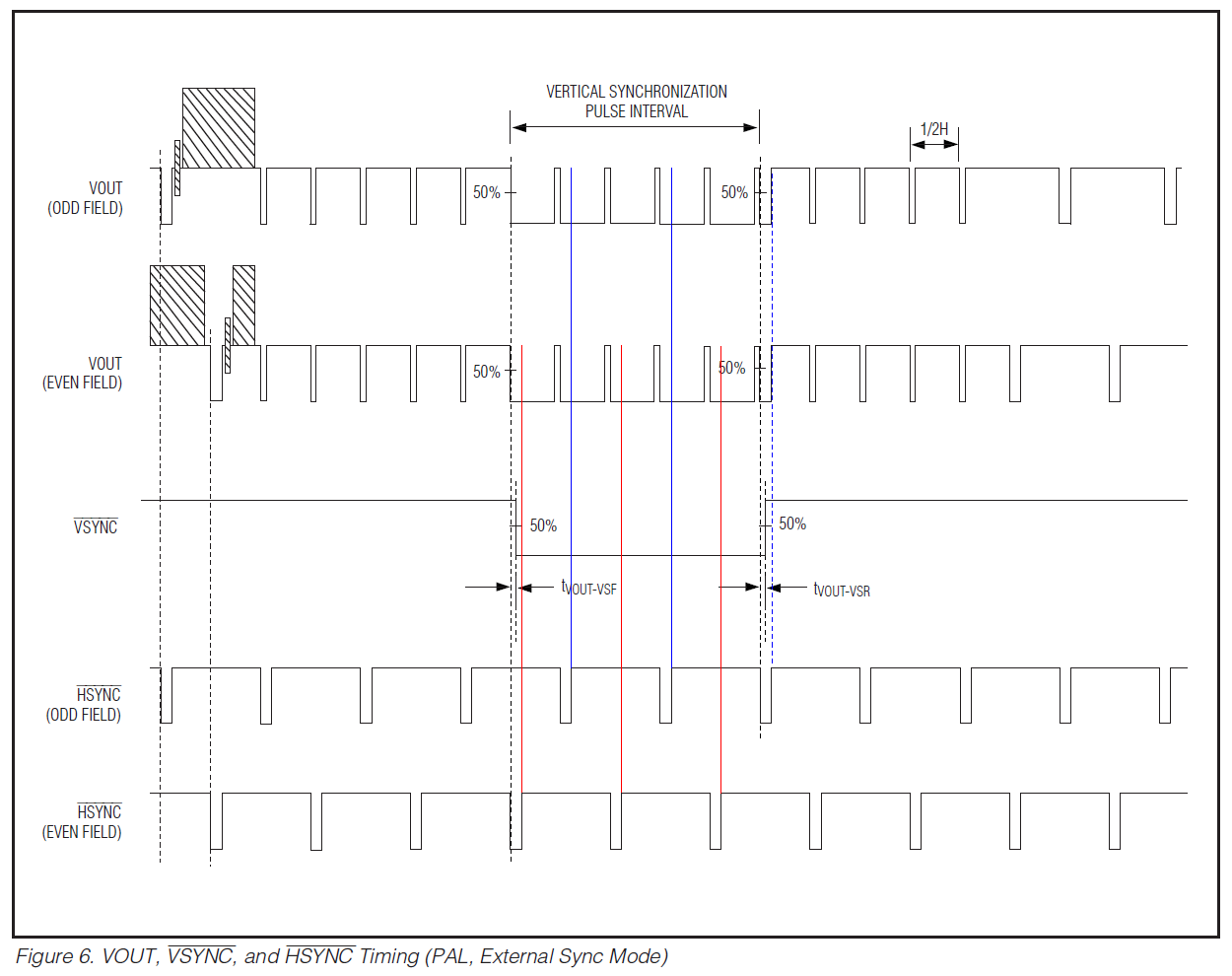

Selon son datasheet, le MAX7456 permet d’incruster 16 lignes de 30 caractères en mode 625 lignes. Le vocable PAL désigne ce dernier mode alors que le vocable NTSC désigne le mode 525 lignes.

Les caractères sont inscrits dans des blocs jointifs de 18 rangées de 12 pixels, la fenêtre de l’OSD a donc une hauteur de 18×16 lignes soit 288 lignes.

Selon la recommandation internationale UIT-R BT.1700, chaque trame comporte 287,5 lignes visibles, la fenêtre OSD déborderait donc d’une demi-ligne en hauteur.

On peut immédiatement en déduire que les caractères affichés auront une hauteur double de celle du générateur, soit 36 lignes, puisque les trames sont entrelacées.

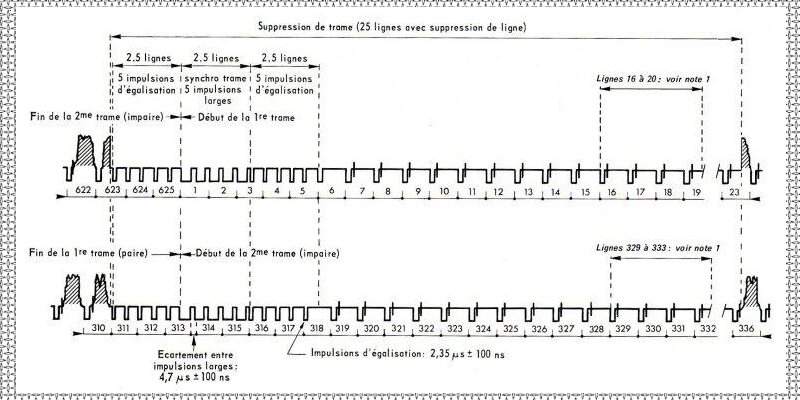

Le signal vidéo standard tel qu’il est défini par la recommandation internationale UIT-R BT.1700 :

- La vidéo visible véhiculée par la première trame ou trame paire débute sur la deuxième moitié de la ligne 23 et s’achève avec la ligne 310,

- La vidéo visible véhiculée par la deuxième trame ou trame impaire débute avec la ligne 336 et s’achève sur la première moitié de la ligne 623.

La trame paire comporte donc ½ + 287 lignes visibles alors que la trame impaire en comporte 287 + ½.

L’affichage d’une image nécessite donc 576 lignes (2 fois 288 ) mais l’affichage réel équivaut à une image de 575 lignes (2 fois 287 + 2 demi lignes ).

Logiquement on devrait s’attendre à ce que le MAX7456 réalise l’incrustation des 288 lignes de la fenêtre OSD en se conformant au plus près de la recommandation précitée :

- Trame paire : pour afficher 288 lignes au lieu des 287,5 lignes usuelles, la ligne 23 devra être complète au lieu de n’en utiliser que la seconde moitié. Cette fenêtre débuterait alors avec une ligne 23 complète et s’achèverait avec la ligne 310.

- Trame impaire : La ligne 623 étant inutilisable car interrompue par une impulsion d’égalisation en son milieu, la ligne 622 devrait lui être alors substituée ce qui aurait pour conséquence de décaler la fenêtre OSD une ligne plus en avant. Cette fenêtre débuterait alors avec la ligne 335 au lieu de la ligne 336 et s’achèverait avec la ligne 622.

Mais ces suppositions, aussi logiques qu’elles soient, doivent être vérifiées car le datasheet du MAX7456 est absolument muet à ce sujet. Une divergence quelconque rendrait alors ce projet impossible.

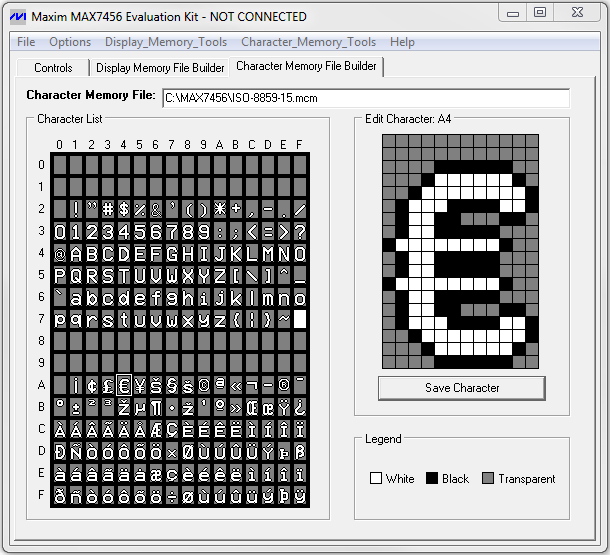

Pour se faire la main avec l’Arduino et le MAX7456, quoi de mieux que de s’exercer avec la reprogrammation des caractères du MAX7456. Ceux prédéfinis à l’origine sont inexploitables, les emplacements du peu de caractères européens ne correspondent pas à leur code ASCII et la foultitude des autres représentent des idéogrammes extrême-orientaux dont l’intérêt est quasi nul.

Pas besoin de réinventer le fil à couper le beure, le net fourmille de sketches appropriés pour effectuer cette reprogrammation, il suffit de les importer dans l’Arduino et de les adapter à ses désidérata si nécessaire.

Afin que cette reprogrammation soit réutilisable avec profit pour d’autres projets, la table de caractères choisie est celle de l’ISO-8859-15 qui comporte tous les caractères européens y compris le sigle de l’euro :

La prise en main une fois effectuée, il est temps de se consacrer aux tests proprement dits :

- La mémoire de l’OSD a été initialisée avec des caractères transparents (l’espace, code 0x20 ) sauf tous ceux de la première et de la dernière ligne qui l’ont été avec le caractère rub-out (code 0x7F ) dont la représentation est celle d’un bloc uniformément blanc.

- Visuellement, il s’affiche donc deux bandes blanches épaisses sur toute la largeur de l’écran, la supérieure tout en haut et l’inférieure tout en bas de la fenêtre.

Le montage de test utilisé pour ausculter le MAX7456 :

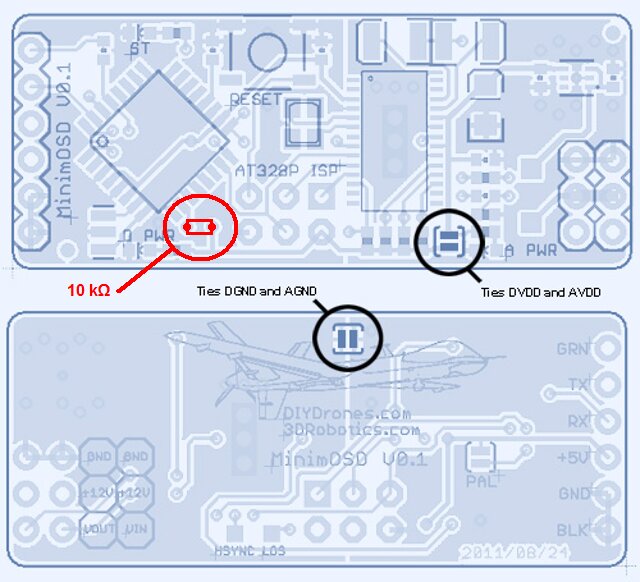

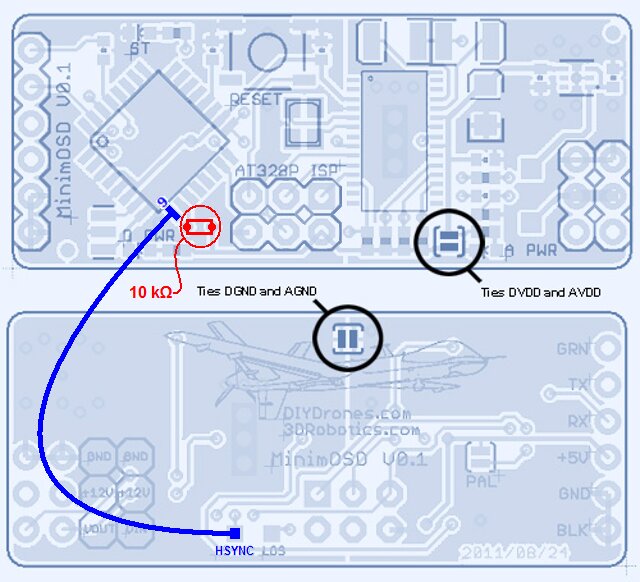

C’est une plaquette minimOSD qui a été utilisé pour ce test, elle inclue le MAX7456 ainsi qu’une puce Arduino ATmega328P. Cependant il est nécessaire de lui adjoindre un « FTDI breakout board » comme celui-ci pour la connecter à l’IDE arduino du PC et par la même occasion alimenter l’ensemble via la connexion USB.

Cette option n’est pas vraiment « plug and play » car il a fallu sortir le fer à souder pour ajouter le connecteur ISP ainsi qu’une résistance de rappel au +5 volts sur le chip select du MAX7456. Il a été aussi nécessaire d’injecter le bootloader Arduino avec un programmateur ISP car la puce en étant dépourvue. Cela reste malgré tout l’option la plus économique.

- Un détecteur de ligne blanche à base d’un sextuple inverseur 74HC14 a été connecté sur la sortiev idéo du MAX7456,

- Les sorties synchro ligne et synchro trame du MAX7456 ainsi que celle du détecteur de ligne blanche ont été connectées sur un petit analyseur logique Scanalogic-2 de chez IKAlogic,

- Aucune source vidéo extérieure n’est nécessaire, c’est le mode synchronisation interne du MAX7456 qui est utilisé pour le test. Une vérification ultérieure a permis de constater que le fonctionnement de l’OSD était le même lorsqu’il se synchronisait sur un signal vidéo extérieur.

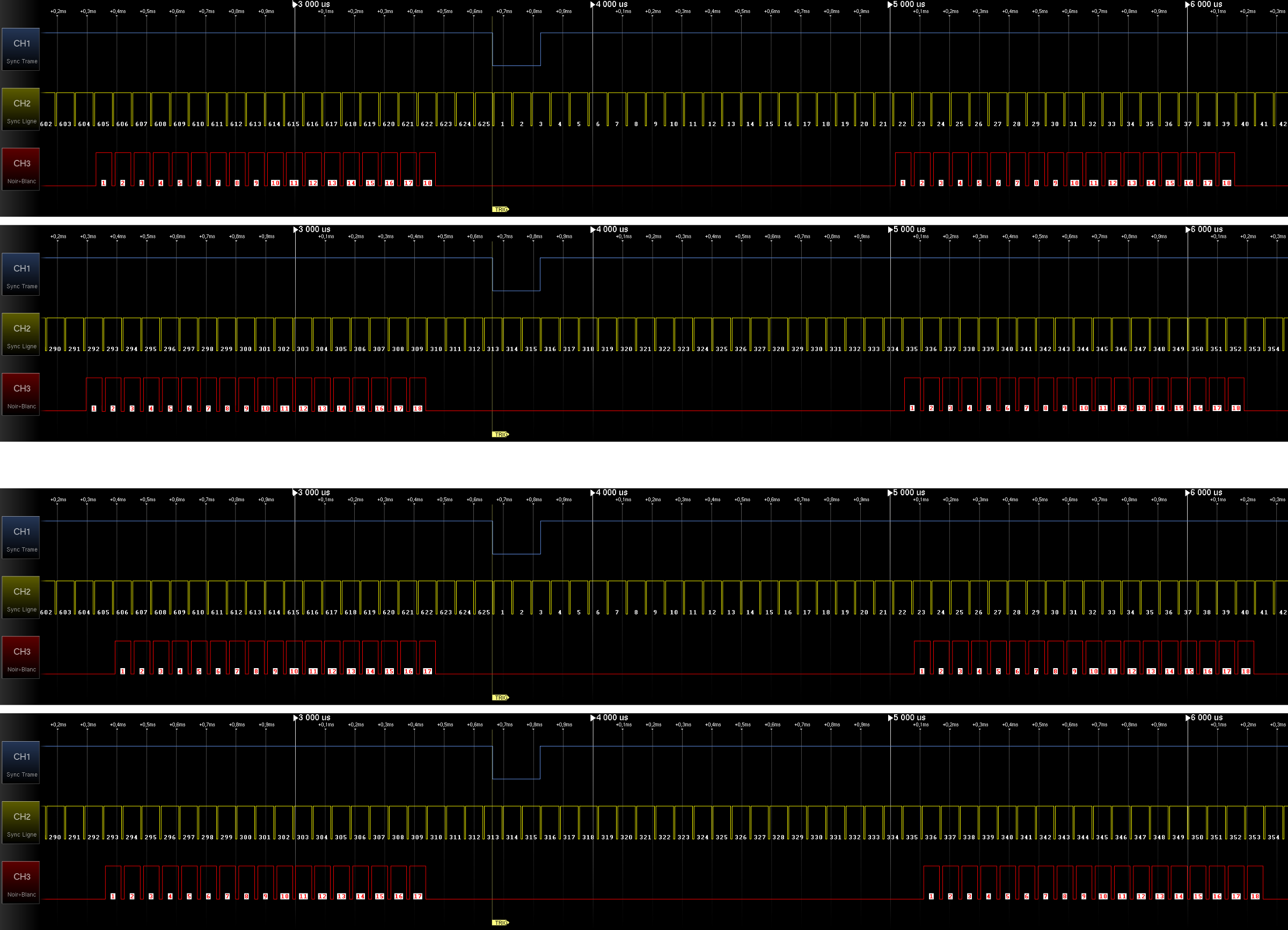

Toutes les images des captures ont été réalisées après initialisation de la mémoire OSD comme décrit plus haut.

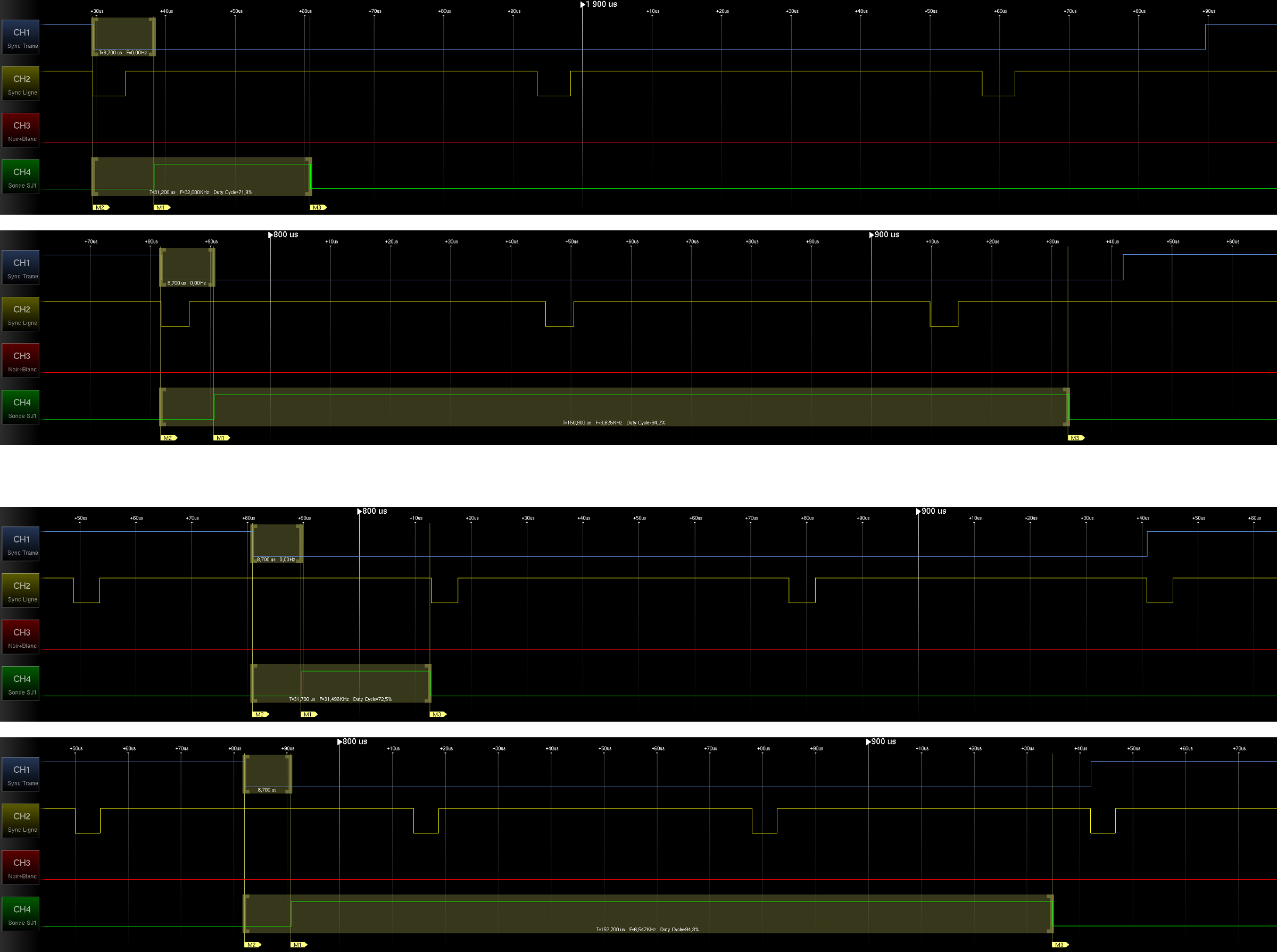

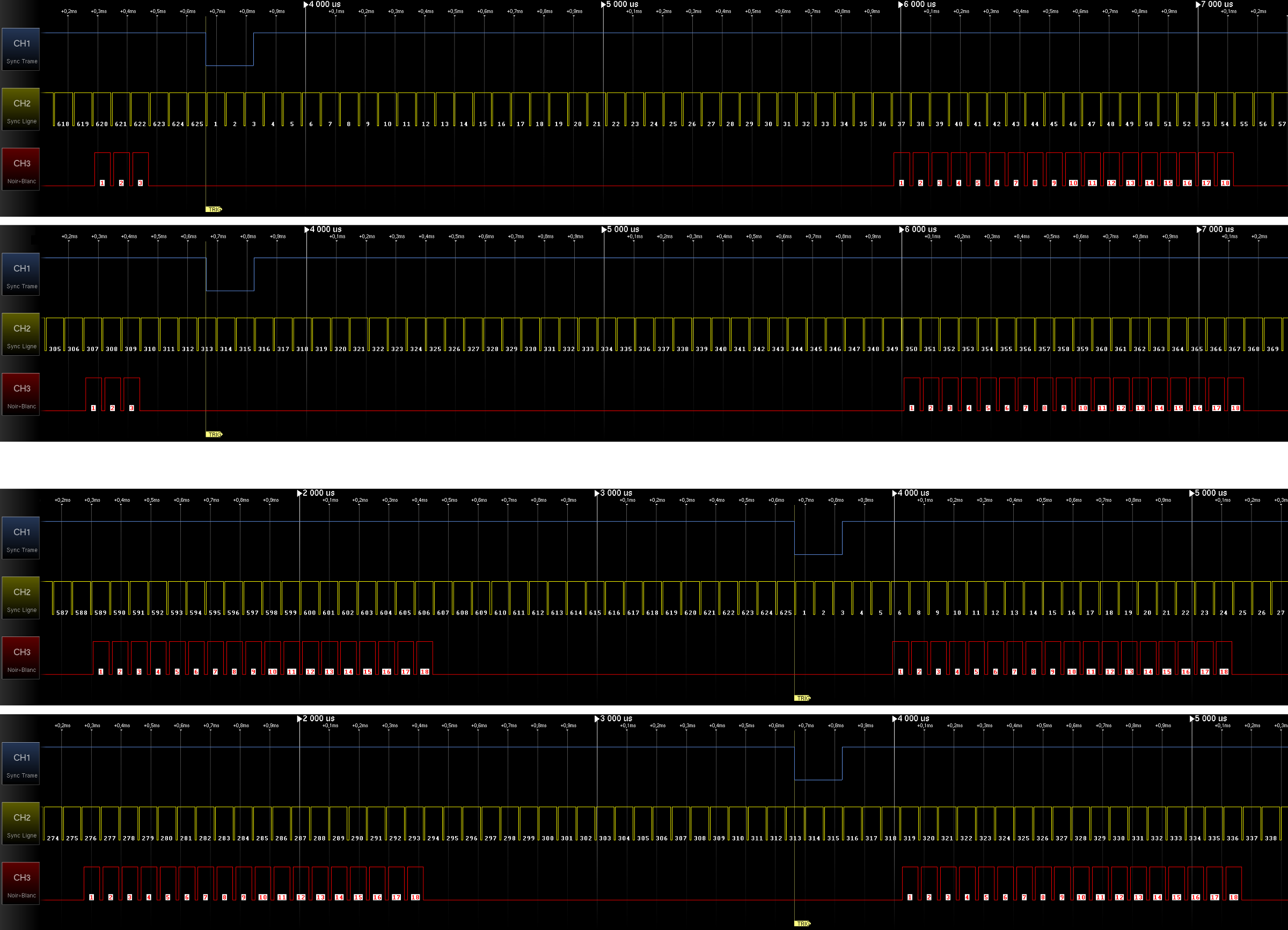

Chaque image regroupe 3 traces:* La trace supérieure bleue est celle de la synchronisation trame,

- La trace centrale jaune est celle de la synchronisation ligne. Les impulsions d’égalisation ont été oblitérées par le MAX7456,

- La trace inférieure rouge est celle du détecteur de niveau. Il devrait y avoir 18 paliers consécutifs au niveau haut de part et d’autre de la synchronisation trame. Ces paliers correspondent aux 18 lignes des bandes blanches épaisses programmées tout en haut et tout en bas d’écran. Chaque palier est constitué par la juxtaposition des pixels d’une même rangée des 30 pavés blancs dont chaque bande est constituée, aucun n’est crevassé puisque les pavés blancs sont tous jointifs.

Premier groupe d’images: cas standard sans aucun offset vertical.

- Image supérieure:* fin de trame impaire : le 18ème palier du détecteur de niveau alias la dernière ligne de la fenêtre OSD correspond bien à la ligne 622 comme cela avait été présenti,

- début de trame paire : le 1er palier du détecteur alias la première ligne de la fenêtre OSD correspond à la ligne 22, mauvaise augure pour la suite du projet, la fenêtre débuterait donc une ligne plus en avant que ce qui aurait été logique d’escompter.

- Image inférieure:* fin de trame paire : le 18ème palier alias la dernière ligne de la fenêtre OSD correspond à la ligne 309, alors qu’il aurait fallu qu’elle se termine avec la ligne 310 comme on était logiquement en droit de l’espérer,

- début de trace impaire : RAS, la fenêtre commence bien sur la ligne 335 comme cela avait été pressenti.

Avec un tel positionnement de la fenêtre OSD dans la trame paire aussi inattendu, car irrespectueux de la recommandation de l’UIT, la poursuite du projet devient problématique. Il ne reste plus qu’un mince espoir avec le registre d’offset du MAX7456 qui permet de déplacer la fenêtre dans la trame jusqu’à 16 lignes plus haut ou 15 lignes plus bas.

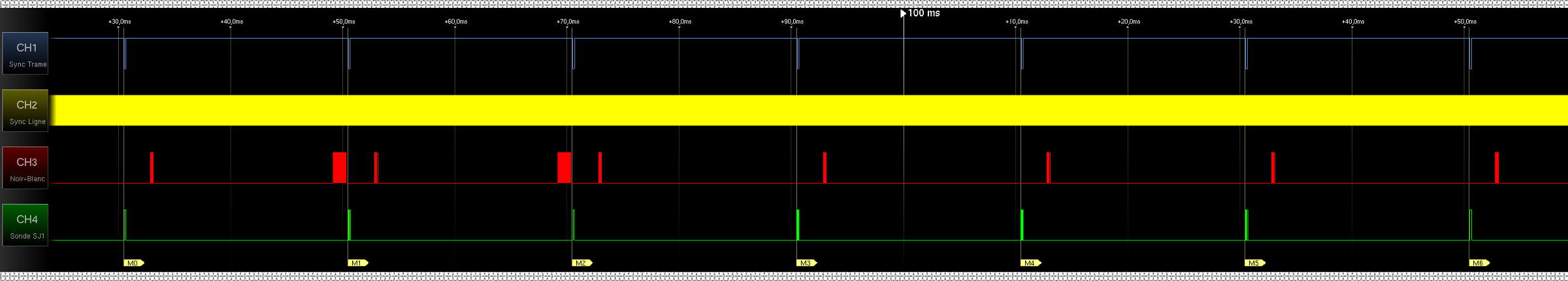

Second groupe d’images: Tentative d’inclure la ligne 310 avec un offset vertical de +1 ligne (registre VOS ):

- Image supérieure:* fin de trame impaire : le 17ème palier du détecteur de niveau alias la pénultième ligne de la fenêtre OSD correspond à la ligne 622. La 18éme et dernière ligne de la fenêtre est oblitérée, ce qui est cohérent car la ligne 623 est crevassé en son milieu par une impulsion d’égalisation. La période de suppression trame du MAX7456 débuterait donc dés la ligne 623,

- début de trame paire : la fenêtre OSD s’est déplacé d’une ligne vers le bas puisque la bande blanche commence maintenant à la ligne 23.

- Image inférieure:* fin de trame paire : le 17ème palier alias la pénultième ligne de la fenêtre OSD correspond à la ligne 309, le 18ème et dernier palier est oblitéré et la ligne 310 reste désespérément vierge, le dernier espoir restant s’est évanoui ! La période de suppression trame du MAX7456 débute donc dés la ligne 310, une ligne beaucoup trop tôt !

- début de trace impaire : la fenêtre OSD s’est déplacé d’une ligne vers le bas puisque la bande blanche commence maintenant à la ligne 336.

Affichage de la fenêtre OSD quand on lui inflige le décalage vertical maximal (+15 et -16 lignes)

Premier groupe d’images: avec offset vertical maximum de +15 lignes :

- Il ne subsiste plus que 3 paliers, la bande blanche du bas est sévèrement amputée puisqu’il ne s’affiche plus que ses 3 premières lignes. Toutes les autres ont été englouties par la période de suppression trame qui s’établit définitivement pour le MAX7456 avec la ligne 310 pour la trame paire et avec la ligne 623 pour la trame impaire.

- La bande blanche du haut est descendue 15 lignes plus bas, la fenêtre OSD s’ouvre maintenant avec les lignes 37 et 350.

Deuxième groupe d’images: avec offset vertical maximum de -16 lignes :

- La bande blanche du bas est remontée 16 lignes plus haut, la fenêtre OSD se referme maintenant sur les lignes 293 et 606,

- La bande blanche du haut s’est déplacée 16 lignes plus haut, la fenêtre OSD s’ouvre maintenant sur les lignes 6 et 319. Il n’est absolument pas garanti qu’un moniteur CRT puisse afficher les premières lignes de la fenêtre avec un tel offset qui frise la dernière impulsion d’égalisation.

Malheureusement cette idée d’utiliser qui semblait pertinente au départ a été mise à mal par la conception interne du MAX7456.

L’impulsion d’égalisation en plein milieu de la ligne 623 qui a imposé l’ouverture de la fenêtre OSD une ligne plutôt dans la trame impaire a dû aussi impacter la trame paire car la même circuiterie interne a dû être utilisée pour toutes les trames quelque soit leur parité sans que cette dernière puisse influencer quoi que ce soit.

Doctsf (Modèles & Marques)

Doctsf (Modèles & Marques) Annonces

Annonces